電気・電子回路における電源回路の基礎 -ツェナーダイオード+トランジスタ(3)-

①はじめに

今回は、ツェナーダイオード+トランジスタで構成したリニアレギュレータ基本回路に帰還制御回路を付加して、動作を調べてみようと思います。

②ツェナーダイオード+トランジスタ

帰還制御基本回路

シミュレーション

シミュレーションファイル「ZD+Tr_帰還制御.asc」を参照してください。

基本回路にトランジスタを1つ追加しただけの極めて簡単な回路ですが、帰還制御の基本的機能を実現しています。

出力電圧は、基本回路の場合にはVout=ツェナー電圧Vz-ベース・エミッタ間電圧VBEです。帰還制御を付加した回路ではVout_1=Vz+VBEとなっています。しかし、こちらのVBEは、帰還制御用トランジスタQ3のVBEであって、出力トランジスタQ2のVBEではありません。出力トランジスタQ2のVBEは、帰還制御作用によって出力電圧には影響しません。

続いて、帰還制御回路の動作を調べてみましょう。

シミュレーション

シミュレーションファイル「ZD+Tr_帰還制御_動作解析.asc」を参照してください。

誤差増幅特性

帰還制御トランジスタQ4のベースと出力Vout_2を切り離し、ベースに試験用電圧V_FBを入力しています。Q4のエミッタにはツェナーダイオードが接続されていますから、V_FBがツェナー電圧(約6.2V)以下では、Q4のベース電流は流れず、コレクタ電流も流れませんので(カットオフ状態)、コレクタ抵抗R3には、出力トランジスタQ5のベース電流のみが流れます。よって、出力Vout_2は、Vout_2=Vin-(R3の電圧降下)-(Q5のVBE)であり、約10.7Vとなっています。

V_FBがツェナー電圧より大きくなると、Q4のベース電流、コレクタ電流が流れ始め、R3の電圧降下が大きくなり、Q4のコレクタ電圧(=Q5のベース電圧)は徐々に低下していき、それに伴い、出力Vout_2も徐々に低下していきます。この傾向は、V_FBが6.88Vあたりで急激な変化となっています。

V_FBがさらに大きくなり、6.9V以上では、Q4は飽和してコレクタ電圧は、ほとんどツェナー電圧と同じ電圧となって、変化しません。したがって、出力もVz-(Q5のVBE)で一定になります。

帰還制御接続では、帰還制御トランジスタQ4のベースと出力Vout_2を接続しますから、同じ電圧となります。つまり、V_FB=Vout_2となる状態で安定することになります。シミュレーションで、Vout_1、V_FB、Vout_2のグラフを表示してください。3つのグラフが同じ電圧で交差していることが確認できます。これを見ると、帰還制御接続の出力電圧=(ツェナー電圧Vz)+(安定状態での帰還制御トランジスタのVBE)となることがわかると思います。

出力トランジスタVBE変動

帰還制御回路の出力電圧には、出力トランジスタのVBEが影響しないことを確認できる回路を用意しました。この回路では、出力トランジスタQ7のベースに電圧源を直列に挿入して±0.1Vの電圧変動を与えています。出力Vout_3を観察してください。ほとんど出力変化が見られません。拡大してみると、±0.8mVほどの変動がみえますが、元の電圧変動を1/100以下のレベルに押さえ込んでいます。

入力変動特性、負荷変動特性

シミュレーション

シミュレーションファイル「ZD+Tr_帰還制御_入力変動特性例.asc」を参照してください。

入力電圧Vinを0~24Vまで変化させています。基本回路と比較して、出力電圧は異なりますが、同様な入力変動特性となっています。

シミュレーション

シミュレーションファイル「ZD+Tr_帰還制御_負荷変動特性例.asc」を参照してください。

負荷電流を0~100mAまで変化させています。入力電圧Vinは12V固定です。基本回路と比較して、格段に改善されています。基本回路の特性は、負荷変動に伴う、出力トランジスタのVBEの変化が原因ですので、この影響を受けない帰還制御であれば、当然の結果と言えます。

今回の一言

次回は、帰還制御トランジスタのVBE補正、その他の発展・改善を試みる予定です。

今回取り上げましたサンプルファイルを使うには、アナログ・デバイセズのサイトよりLTspiceをダウンロードしてご利用下さい。

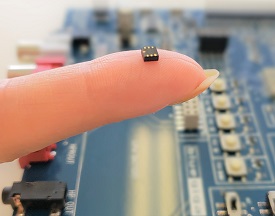

国内初!!超小型、6V入力DC/DCコンバータ新登場!!

業界最小サイズ!:独自開発のパッケージングで実装面積は3mm×3mm、厚さ1.4mm

抜群の変換効率!:最大90%以上

詳細は ここ をクリック

ご興味、ご関心のある方は「お問い合わせ」をクリックの上、ご連絡下さい。